集成电路技术的未来挑战与发展方向

集成电路(Integrated Circuit, IC),作为现代信息社会的基石,已渗透到从个人消费电子到国防军工、从工业控制到尖端科研的每一个角落。其发展遵循着著名的“摩尔定律”已逾半个世纪,但随着晶体管尺寸逼近物理极限,单纯依靠工艺微缩的路径正面临前所未有的挑战。集成电路技术的发展必须兼顾延续“摩尔定律”的微缩路径与超越“摩尔定律”的创新路径,迎接挑战并开拓新的发展方向。

未来挑战:多重极限的逼近

- 物理极限:当晶体管特征尺寸进入纳米尺度(如3纳米及以下)后,量子隧穿效应等物理现象愈发显著,导致漏电流激增、功耗失控、器件稳定性下降。传统的硅基CMOS技术正在触及材料与物理原理的根本边界。

- 技术极限:极紫外光刻(EUV)等先进制造设备的复杂度与成本呈指数级增长,建设一座先进晶圆厂的投入已高达数百亿美元。工艺步骤多达数千步,良率提升和缺陷控制变得极其困难。

- 功耗墙与存储墙:芯片性能提升的功耗密度急剧上升,“功耗墙”问题严峻,尤其在数据中心和移动设备中。处理器与存储器之间的速度差距(即“存储墙”)已成为制约系统整体性能的主要瓶颈。

- 设计复杂性:集成数十亿甚至上千亿个晶体管,使得芯片设计复杂度爆炸性增长。从架构设计、逻辑综合到物理实现与验证,整个设计流程面临巨大的时间、人力和计算资源压力。

- 供应链安全与地缘政治:全球集成电路产业高度分工,任何环节的断裂(如高端光刻机、关键IP、特种材料)都可能引发供应链危机。地缘政治因素进一步加剧了技术获取和产业合作的不确定性。

发展方向:多维度的创新与演进

面对上述挑战,集成电路技术正朝着“More Moore”(延续摩尔)和“More than Moore”(超越摩尔)两个维度协同演进。

一、 延续摩尔(More Moore):深入微观,探索新器件与新工艺

- 新器件结构:继续探索全环绕栅极晶体管、互补场效应晶体管等先进架构,以更好地控制沟道电流。

- 新材料引入:在晶体管沟道中引入高迁移率材料(如锗硅、III-V族化合物),在互联层引入新型低电阻率金属(如钌、钴)及低k介质材料。

- 三维集成:从芯片层面的3D NAND存储,走向晶体管层面的立体堆叠(如CFET),通过在垂直方向堆叠器件来延续集成度提升。

- 先进封装与系统集成:将不同工艺节点、不同功能的芯粒通过硅中介层、再布线层等技术进行高密度集成,形成异构系统级封装,这是短期内提升系统性能与能效的关键路径。

二、 超越摩尔(More than Moore):拓展功能,实现异质融合

- 异构集成:将计算、存储、传感、射频、功率管理等不同功能的芯片或模块集成在一个封装内,实现“感、算、存、传、供”一体化。

- 新计算范式芯片:针对人工智能、类脑计算等特定场景,发展专用集成电路、存算一体芯片、神经拟态芯片等,打破传统冯·诺依曼架构的瓶颈。

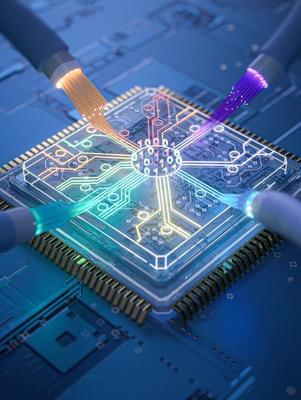

- 光子集成:利用光信号进行芯片内或芯片间的高速数据传输,有望彻底解决电互联的带宽和功耗问题,是未来高性能计算和通信的核心方向之一。

- 宽禁带半导体器件:基于氮化镓、碳化硅的功率和射频器件,在新能源汽车、5G/6G通信、智能电网等领域发挥着不可替代的作用,是功能拓展的重要分支。

三、 设计方法与生态革新

- EDA工具智能化:利用人工智能与机器学习优化芯片设计流程,进行自动布局布线、功耗预测、良率优化,大幅提升设计效率。

- 开源生态建设:发展开源硬件指令集、开源EDA工具和开源IP,降低芯片设计门槛,促进创新。

- 软硬件协同设计:从应用和算法出发,反向定义芯片架构,实现极致的能效比,如各大科技公司自研的AI芯片。

###

集成电路技术的已不再是一条单一的微缩赛道,而是一个多维创新、多技术融合的广阔疆域。挑战虽严峻,但通过材料、器件、架构、封装、设计方法乃至产业生态的全面创新,集成电路产业必将突破瓶颈,持续驱动新一轮的科技革命和产业变革,为智能世界构建更强大、更高效、更多元的数字基石。

最新产品

强芯联盈,康佳芯盈与联强国际达成战略合作,开启集成电路产业全新篇章

解析10mq060ntrpbf 一款高性能集成电路的应用与特性

高速发展!西部(重庆)科学城集成电路产业谱写“芯”篇章

硅基光电子新突破 低损耗光纤水平硅晶圆光导问世,为下一代光子集成电路发展注入强劲动力

多份报告展现中国创新链实力与潜力,行业投向“硬科技”特色凸显,集成电路成核心引擎

纺织新革命 将集成电路“印”在布料上

HY6264ALJ-10IC 集成电路 关键特性与应用领域详解

省奖揭晓!我市斩获集成电路领域唯一殊荣,领跑优势再获印证

集成电路技术的未来挑战与发展方向

2025中国上海国际集成电路与半导体产业展览会 洞察未来芯格局,共筑产业新高地